20210617 / 數位時代 採訪中心

台積電衝刺先進製程,在6月技術論壇對3奈米以下的先進製程提出藍圖,成為半導體市場熱切關注的焦點。

據台積電指出,3奈米將於2022年下半年量產,將相較於前代提升15%效能、降低30%功耗。於此同時,應用材料、新思科技也分別於17日發佈最新解決方案、最新認證消息,將有助於台積電衝刺3奈米製程。

應用材料:新佈線工程設計助攻晶片表現

應用材料宣布,全新的佈線工程設計解決方案Endura Copper Barrier Seed IMS(銅阻障層晶種整合),將可讓先進邏輯晶片縮制3奈米或是更小的尺寸,並提升晶片性能、降低功耗。

針對此解決方案,應用材料指出,雖然尺寸減小有利於晶體管性能,但互聯佈線的情況卻恰好相反;因較小的佈線會有更大電阻,將降低性能並增加功耗。從7奈米微縮至3奈米節點,互聯通孔電子將增加10倍,若是沒有材料工程從中突破,將會抵消晶體館縮放的優勢。

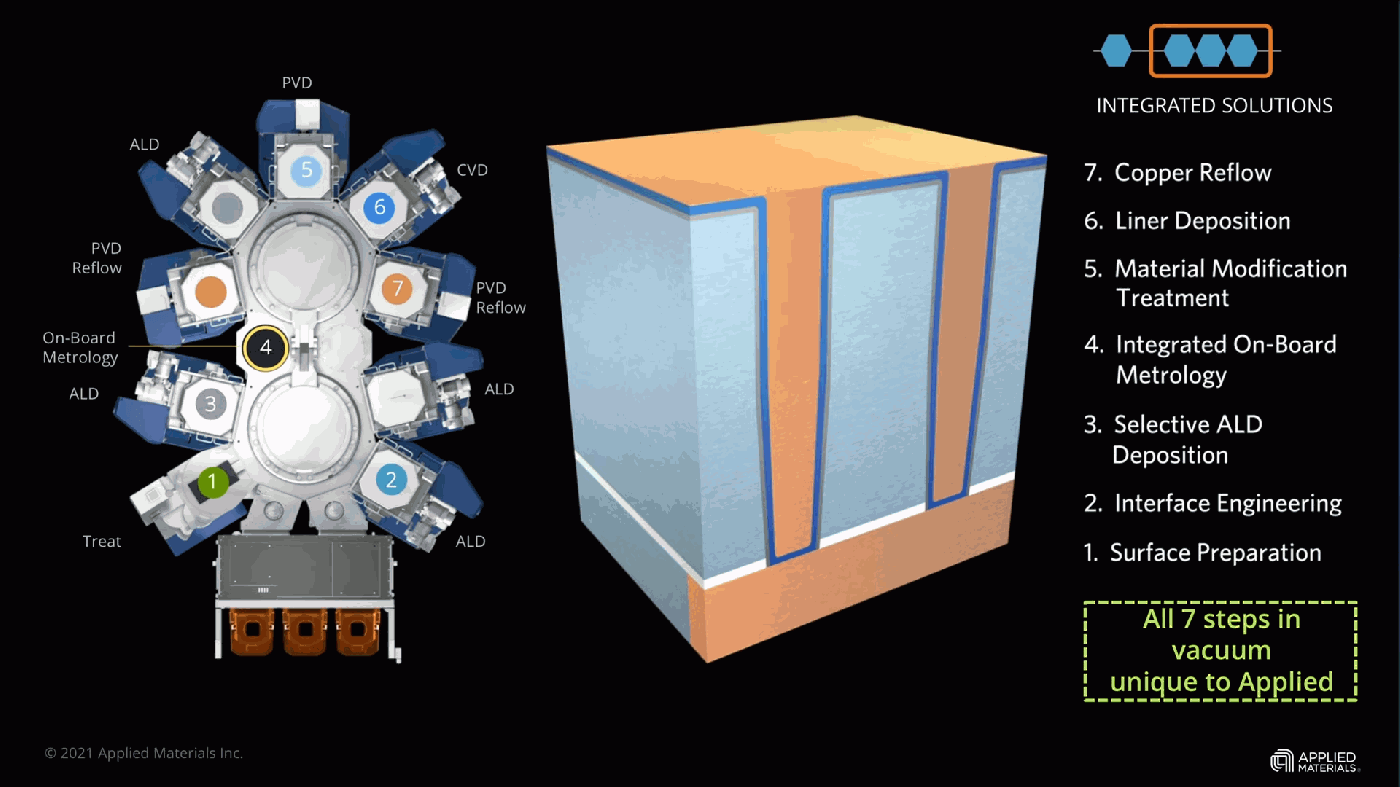

這項整合式材料解決方案,即為在高真空環境下,將7種不同製程至數整合至同一套系統。其中包含ALD (原子層沉積)、PVD (物理氣相沉積)、CVD (化學氣相沉積)、銅回流、表面處理、介面工程和量測。

應材針對3奈米製程提出整合式材料解決方案,在高真空環境下,將7種不同製程至數整合至同一套系統。 圖片來源/應用材料

這樣的組合也使用選擇性『原子層沉積』取代共行性,可以消除通路介面處的高電阻率阻障層。

除此之外,這項解決方案也涵蓋銅回流技術,可以實現無空隙間隙填充。通孔接觸面的電阻也降低多達50%,如此一來,就提升了晶片性能和功耗,讓邏輯縮放能夠持續至3奈米以上。

為何這樣的作法能夠提升晶片表現?應用材料高級副總裁暨半導體產品事業部總經理Prabu Raja點出:「一個智慧型手機的晶片有數百億條銅線互連,佈線已消耗晶片三分之一的功率;而在真空中集成多種工藝技術,可使我們重新設計材料和結構,以便消費者擁有功能更強大的設備、更長的電池壽命。」

Raja指出,這種獨特的整合式解決方案可以加快我們客戶的性能、功耗和面積成本的技術藍圖。

新思科技:解決方案獲3奈米製程認證

針對台積電最先進3奈米製程,新思科技也提出數位與客製化解決方案,已獲3奈米製程技術DRM與SPICE模型認證。

美國電子設計自動化公司新思科技。圖片來源/ 新思科技官網

新思科技提出的數位與客製化解決方案已通過台積公司最新設計參考流程 (design-rule manual,DRM)及製程設計套件(process design kits)的認證。

據悉,該認證將提供共同優化的工具、流程和方法,讓客戶實現製程效能和面積 (PPA)表現,加速新一代高效能運算(HPC)、行動、5G和AI 晶片設計的創新。

新思科技指出,透過高度整合的融合設計平台(Fusion Design Platform)和客製化設計平台(Custom Design Platform),讓雙方客戶可從台積電先進製程技術實現最大效益。

而新思科技與台積電在3奈米製程的合作,除了在先進佈線技術、也包括低電壓變動支援、支援台積電的佈局(placement)規則。

台積電設計建構管理處副總經理Suk Lee表示:「台積公司的先進技術需要全新層次的EDA協作與創新,以實現3奈米製程技術的高效能和低功耗目標。」他補充,將與海思科技持續密切合作,為HPC、行動、5G和AI應用實現新一代的設計。

責任編輯:錢玉紘

文章出處: 數位時代